### **VNP10N06**

# "OMNIFET": FULLY AUTOPROTECTED POWER MOSFET

| TYPE     | V <sub>clamp</sub> | R <sub>DS(on)</sub> | l <sub>lim</sub> |

|----------|--------------------|---------------------|------------------|

| VNP10N06 | 60 V               | 0.3 Ω               | 10 A             |

- LINEAR CURRENT LIMITATION

- THERMAL SHUT DOWN

- SHORT CIRCUIT PROTECTION

- INTEGRATED CLAMP

- LOW CURRENT DRAWN FROM INPUT PIN

- LOGIC LEVEL INPUT THRESHOLD

- ESD PROTECTION

- SCHMITT TRIGGER ON INPUT

- HIGH NOISE IMMUNITY

- STANDARD TO-220 PACKAGE

#### **DESCRIPTION**

The VNP10N06 is a monolithic device made using STMicroelectronics VIPower Technology, intended for replacement of standard power MOSFETS in DC to 50 KHz applications. Built-in thermal shut-down, linear current limitation and overvoltage clamp protect the chip n harsh environments.

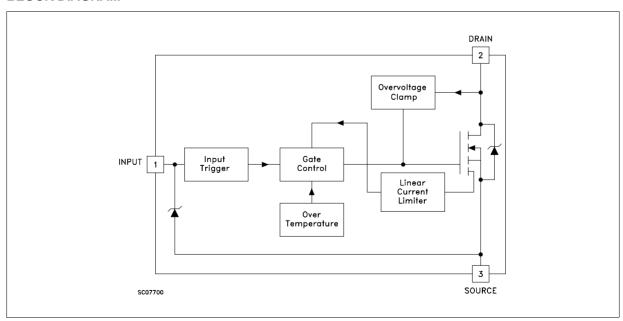

#### **BLOCK DIAGRAM**

March 2004 1/11

#### **ABSOLUTE MAXIMUM RATING**

| Symbol           | Parameter                                     | Value              | Unit |

|------------------|-----------------------------------------------|--------------------|------|

| V <sub>DS</sub>  | Drain-source Voltage (V <sub>in</sub> = 0)    | Internally Clamped | V    |

| V <sub>in</sub>  | Input Voltage                                 | Internally Clamped | V    |

| lin              | Input Current                                 | ± 20               | mA   |

| I <sub>D</sub>   | Drain Current                                 | Internally Limited | А    |

| I <sub>R</sub>   | Reverse DC Output Current                     | -15                | А    |

| V <sub>esd</sub> | Electrostatic Discharge (C= 100 pF, R=1.5 KΩ) | 4000               | V    |

| P <sub>tot</sub> | Total Dissipation at T <sub>c</sub> = 25 °C   | 42                 | W    |

| Tj               | Operating Junction Temperature                | Internally Limited | °C   |

| T <sub>c</sub>   | Case Operating Temperature                    | Internally Limited | °C   |

| T <sub>stg</sub> | Storage Temperature                           | -55 to 150         | °C   |

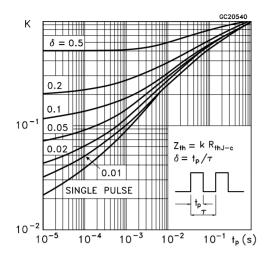

#### THERMAL DATA

| R <sub>thj-case</sub> | Thermal Resistance Junction-case    | Max | 3    | °C/W | l |

|-----------------------|-------------------------------------|-----|------|------|---|

| $R_{thj-amb}$         | Thermal Resistance Junction-ambient | Max | 62.5 | °C/W | Ì |

## **ELECTRICAL CHARACTERISTICS** ( $T_{case} = 25$ $^{o}C$ unless otherwise specified) OFF

| Symbol             | Parameter                                                 | Test Conditions                                                                                                      | Min.    | Тур. | Max.       | Unit     |

|--------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------|------|------------|----------|

| V <sub>CLAMP</sub> | Drain-source Clamp<br>Voltage                             | I <sub>D</sub> = 200 mA V <sub>in</sub> = 0                                                                          | 50      | 60   | 70         | V        |

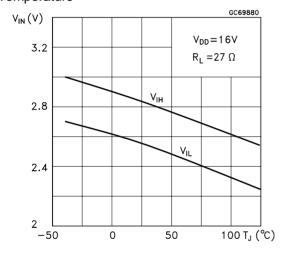

| V <sub>IL</sub>    | Input Low Level<br>Voltage                                | I <sub>D</sub> = 100 μA   V <sub>DS</sub> = 16 V                                                                     |         |      | 1.5        | V        |

| V <sub>IH</sub>    | Input High Level<br>Voltage                               | $R_L = 27 \Omega$ $V_{DD} = 16 V$<br>$V_{DS} = 0.5 V$                                                                | 3.2     |      |            | V        |

| VINCL              | Input-Source Reverse<br>Clamp Voltage                     | l <sub>in</sub> = -1 mA<br>l <sub>in</sub> = 1 mA                                                                    | -1<br>8 |      | -0.3<br>11 | V<br>V   |

| I <sub>DSS</sub>   | Zero Input Voltage<br>Drain Current (V <sub>in</sub> = 0) | V <sub>DS</sub> = 50 V V <sub>in</sub> = V <sub>IL</sub><br>V <sub>DS</sub> < 35 V V <sub>in</sub> = V <sub>IL</sub> |         |      | 250<br>100 | μA<br>μA |

| l <sub>ISS</sub>   | Supply Current from Input Pin                             | V <sub>DS</sub> = 0 V V <sub>in</sub> = 5 V                                                                          |         | 150  | 300        | μΑ       |

### ON (\*)

| Symbol              | Parameter                         | Test Conditions                                                         | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------|-------------------------------------------------------------------------|------|------|------|------|

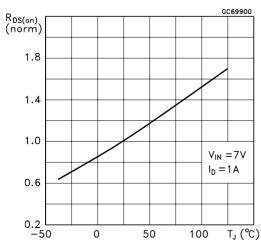

| R <sub>DS(on)</sub> | Static Drain-source On Resistance | $V_{in} = 7 \text{ V}$ $I_D = 1 \text{ A}$ $T_J < 125 ^{\circ}\text{C}$ |      | 0.15 | 0.3  | Ω    |

#### **DYNAMIC**

| Symbol    | Parameter          | Test Conditions                                | Min. | Тур. | Max. | Unit |

|-----------|--------------------|------------------------------------------------|------|------|------|------|

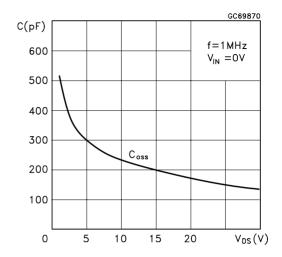

| $C_{oss}$ | Output Capacitance | $V_{DS} = 13 \text{ V}$ f = 1 MHz $V_{in} = 0$ |      | 350  | 500  | pF   |

### **ELECTRICAL CHARACTERISTICS** (continued)

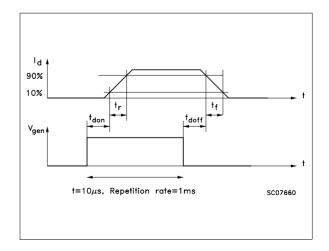

SWITCHING (\*\*)

| Symbol                | Parameter             | Test Conditions                                                      | Min. | Тур. | Max. | Unit |

|-----------------------|-----------------------|----------------------------------------------------------------------|------|------|------|------|

| t <sub>d(on)</sub>    | Turn-on Delay Time    | V <sub>DD</sub> = 16 V I <sub>d</sub> = 1 A                          |      | 1100 | 1600 | ns   |

| tr                    | Rise Time             | $V_{gen} = 7 V$ $R_{gen} = 10 \Omega$                                |      | 550  | 900  | ns   |

| t <sub>d(off)</sub>   | Turn-off Delay Time   | (see figure 3)                                                       |      | 200  | 400  | ns   |

| t <sub>f</sub>        | Fall Time             |                                                                      |      | 100  | 200  | ns   |

| t <sub>d(on)</sub>    | Turn-on Delay Time    | V <sub>DD</sub> = 16 V I <sub>d</sub> = 1 A                          |      | 1.2  | 1.8  | μs   |

| tr                    | Rise Time             | $V_{gen} = 7 \text{ V}$ $R_{gen} = 1000 \Omega$                      |      | 1    | 1.5  | μs   |

| t <sub>d(off)</sub>   | Turn-off Delay Time   | (see figure 3)                                                       |      | 1.6  | 2.3  | μs   |

| t <sub>f</sub>        | Fall Time             |                                                                      |      | 1.2  | 1.8  | μs   |

| (di/dt) <sub>on</sub> | Turn-on Current Slope | V <sub>DD</sub> = 16 V I <sub>D</sub> = 1 A                          |      | 1.5  |      | A/μs |

|                       |                       | $V_{in} = 7 V$ $R_{gen} = 10 \Omega$                                 |      |      |      |      |

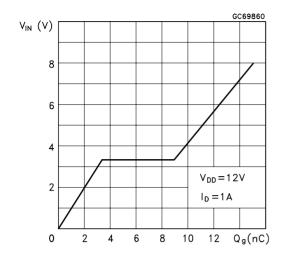

| $Q_{i}$               | Total Input Charge    | $V_{DD} = 12 \text{ V}$ $I_{D} = 1 \text{ A}$ $V_{in} = 7 \text{ V}$ |      | 13   |      | nC   |

#### SOURCE DRAIN DIODE

| Symbol                | Parameter                   | Test Conditions                | Min. | Тур. | Max. | Unit |

|-----------------------|-----------------------------|--------------------------------|------|------|------|------|

| V <sub>SD</sub> (*)   | Forward On Voltage          | $I_{SD} = 1 A V_{in} = V_{IL}$ |      | 0.8  | 1.6  | V    |

| t <sub>rr</sub> (**)  | Reverse Recovery<br>Time    | $I_{SD} = 1 \text{ A}$         |      | 125  |      | ns   |

| Q <sub>rr</sub> (**)  | Reverse Recovery<br>Charge  | (see test circuit, figure 5)   |      | 0.22 |      | μC   |

| I <sub>RRM</sub> (**) | Reverse Recovery<br>Current |                                |      | 3.5  |      | Α    |

#### **PROTECTION**

| Symbol                 | Parameter                        | Test Conditions                                                                          | Min. | Тур. | Max. | Unit |

|------------------------|----------------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| l <sub>lim</sub>       | Drain Current Limit              | V <sub>in</sub> = 7 V V <sub>DS</sub> = 13 V                                             | 6    | 10   | 15   | Α    |

| t <sub>dlim</sub> (**) | Step Response<br>Current Limit   | $V_{in} = 7 \text{ V}$ $V_{DS}$ step from 0 to 13 V                                      |      | 12   | 20   | μs   |

| T <sub>jsh</sub> (**)  | Overtemperature<br>Shutdown      |                                                                                          | 150  |      |      | °C   |

| T <sub>jrs</sub> (**)  | Overtemperature Reset            |                                                                                          | 135  |      |      | °C   |

| Eas (**)               | Single Pulse<br>Avalanche Energy | starting $T_j = 25$ °C $V_{DD} = 24$ V $V_{in} = 7$ V $R_{gen} = 1$ K $\Omega$ L = 10 mH | 250  |      |      | mJ   |

<sup>(\*)</sup> Pulsed: Pulse duration = 300 µs, duty cycle 1.5 % (\*\*) Parameters guaranteed by design/characterization

#### **PROTECTION FEATURES**

During Normal Operation, the INPUT pin is electrically connected to the gate of the internal power MOSFET through a low impedance path as soon as  $V_{\text{IN}} > V_{\text{IH}}$ .

The device then behaves like a standard power MOSFET and can be used as a switch from DC to 50KHz. The only difference from the user's standpoint is that a small DC current (typically 150  $\mu\text{A})$  flows into the INPUT pin in order to supply the internal circuitry.

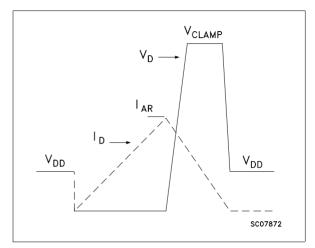

During turn-off of an unclamped inductive load the output voltage is clamped to a safe level by an integrated Zener clamp between DRAIN pin and the gate of the internal Power MOSFET.

In this condition, the Power MOSFET gate is set

to a voltage high enough to sustain the inductive load current even if the INPUT pin is driven to 0V. The device integrates an active current limiter circuit which limits the drain current  $I_D$  to  $I_{lim}$  whatever the INPUT pin Voltage.

When the current limiter is active, the device operates in the linear region, so power dissipation may exceed the heatsinking capability. Both case and junction temperatures increase, and if this phase lasts long enough, junction temperature may reach the overtemperature threshold  $T_{\rm jsh}$ .

If  $T_j$  reaches  $T_{jsh}$ , the device shuts down whatever the INPUT pin voltage. The device will restart automatically when  $T_j$  has cooled down to  $T_{irs}$

#### Thermal Impedance

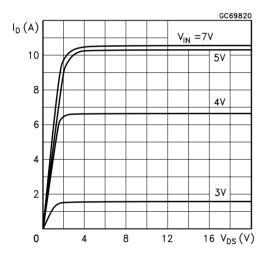

#### **Output Characteristics**

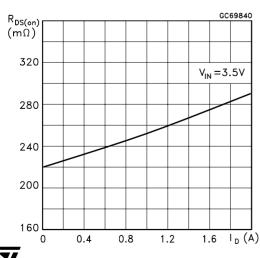

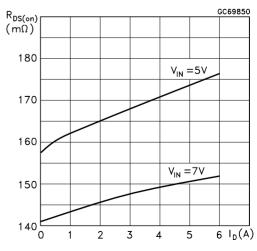

#### Static Drain-Source On Resistance

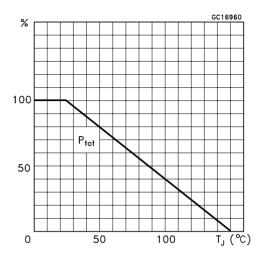

#### **Derating Curve**

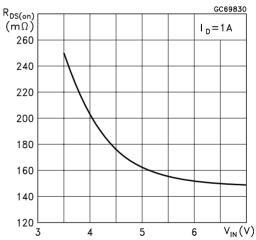

## Static Drain-Source On Resistance vs Input Voltage

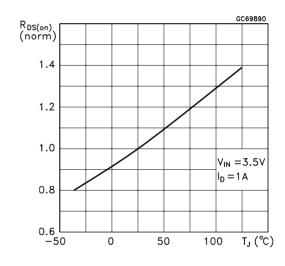

#### Static Drain-Source On Resistance

**577**

#### Input Charge vs Input Voltage

## Normalized Input Threshold Voltage vs Temperature

#### Normalized On Resistance vs Temperature

#### Capacitance Variations

#### Normalized On Resistance vs Temperature

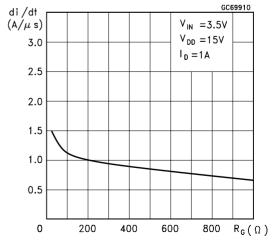

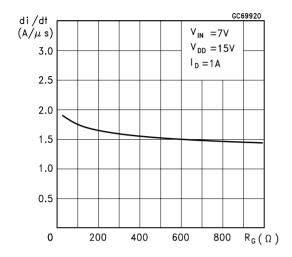

Turn-on Current Slope

4

#### Turn-on Current Slope

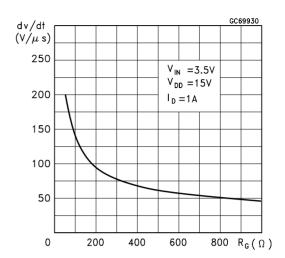

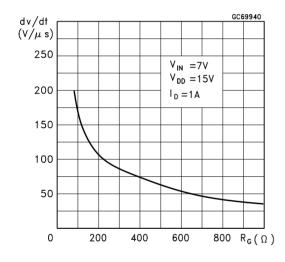

#### Turn-off Drain-Source Voltage Slope

#### Turn-off Drain-Source Voltage Slope

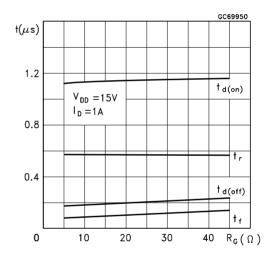

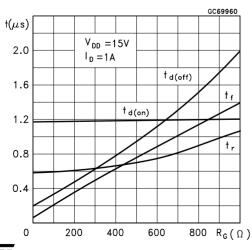

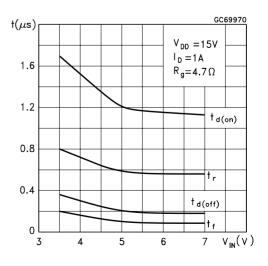

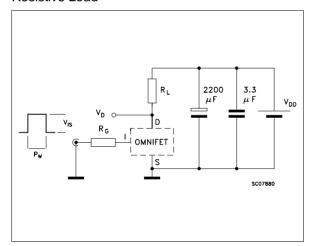

Switching Time Resistive Load

#### Switching Time Resistive Load

#### Switching Time Resistive Load

*5*7

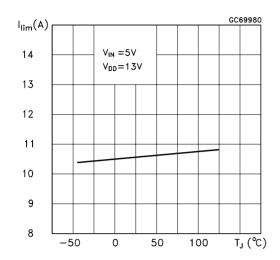

#### Current Limit vs Junction Temperature

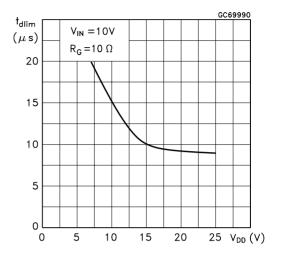

#### Step Response Current Limit

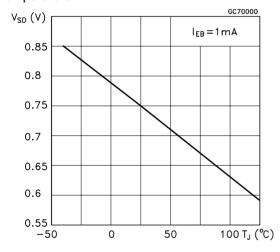

## Source Drain Diode Voltage vs Junction Temperature

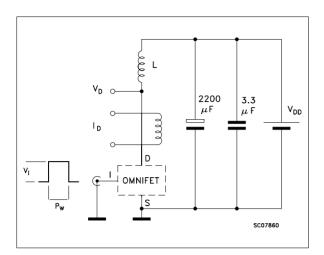

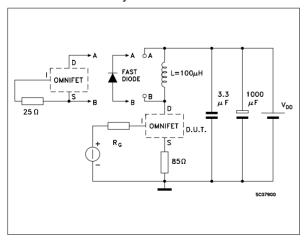

Fig. 1: Unclamped Inductive Load Test Circuits

**Fig. 3:** Switching Times Test Circuits For Resistive Load

**Fig. 5:** Test Circuit For Inductive Load Switching And Diode Recovery Times

Fig. 2: Unclamped Inductive Waveforms

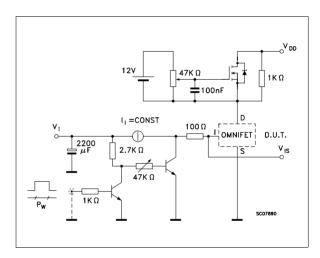

Fig. 4: Input Charge Test Circuit

Fig. 6: Waveforms

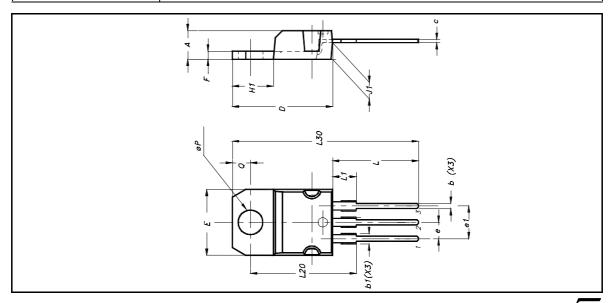

### **TO-220 MECHANICAL DATA**

| DIM            |               | mm.   |       |  |  |

|----------------|---------------|-------|-------|--|--|

| DIM.           | MIN.          | TYP   | MAX.  |  |  |

| A              | 4.40          |       | 4.60  |  |  |

| b              | 0.61          |       | 0.88  |  |  |

| b1             | 1.15          |       | 1.70  |  |  |

| С              | 0.49          |       | 0.70  |  |  |

| D              | 15.25         |       | 15.75 |  |  |

| E              | 10            |       | 10.40 |  |  |

| е              | 2.40          |       | 2.70  |  |  |

| e1             | 4.95          |       | 5.15  |  |  |

| F              | 1.23          |       | 1.32  |  |  |

| H1             | 6.20          |       | 6.60  |  |  |

| J1             | 2.40          |       | 2.72  |  |  |

| L              | 13            |       | 14    |  |  |

| L1             | 3.50          |       | 3.93  |  |  |

| L20            |               | 16.40 |       |  |  |

| L30            |               | 28.90 |       |  |  |

| ØP             | 3.75          |       | 3.85  |  |  |

| Q              | 2.65          |       | 2.95  |  |  |

| Package Weight | 1.9Gr. (Typ.) |       |       |  |  |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a trademark of STMicroelectronics

$\ensuremath{\texttt{©}}$  2004 STMicroelectronics - Printed in ITALY- All Rights Reserved.

#### STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com